|

||||||||||||

|

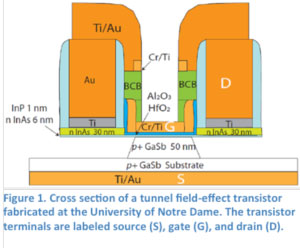

MIND News Notre Dame researchers report dual approach to achieving record TFET device performance February 1, 2013 - Researchers at the University of Notre Dame have produced tunnel field effect transistors (TFETs) with record-high drive current. The results were presented on December 12 at the International Electron Devices Meeting (IEDM 2012) in San Francisco [G. Zhou et al, IEDM 2012, session 32.6]. Complementary metal oxide semiconductor (CMOS) transistors are the building blocks of silicon-based digital, analog, and mixed-signal electronics. However, CMOS technology is approaching fundamental limits that prohibit further miniaturization. TFETs can deliver subthreshold swing lower than the thermal limit (60 mV/decade at room temperature) and thus operate at a supply voltage lower than today's CMOS technology.

The reported approach in realizing TFETs with record performance builds on previous work at Notre Dame, where the team created a new vertical structure. The new findings reported at IEDM show how to improve the TFET on-current in two ways. First, the team adopted a heterojunction based on indium arsenide (InAs) and gallium antimonide (GaSb). This heterojunction in the bulk form has a broken-gap energy band alignment, a very special band alignment that allows electrons to flow freely between the conduction band of InAs and the valence band of GaSb.

Second, a novel device structure and process flow was designed to minimize the effects of parasitic resistances, thus improving the device characteristics. The demonstrated record performance in tunnel FETs improved understanding of the device physics, which should portend more advances in the coming years. The Notre Dame TFET team includes graduate students Guangle Zhou, Tim Vasen, Meng Qi and Yeqing Lu; postdoctoral research associates Rui Li and Qin Zhang; research associate Soo Doo Chae; and professors Thomas Kosel, Mark Wistey, Patrick Fay, Alan Seabaugh and Huili Grace Xing. Contact: Huili Grace Xing, hxing@nd.edu or (574) 631-9108 |

||||||||||||

"TFETs have the potential to significantly lower power consumption in future generation electronics, however, a major issue is their relatively low on-currents," says

"TFETs have the potential to significantly lower power consumption in future generation electronics, however, a major issue is their relatively low on-currents," says  However, in a thin slab of InAs electrostatically controlled by a gate on top (see device cross section), the energy band alignment to the underlying GaSb can be tuned by the gate voltage to be staggered (low tunneling probability) or broken-gap (high tunneling probability), thus enabling more efficient control of tunneling and enable high on-current.

However, in a thin slab of InAs electrostatically controlled by a gate on top (see device cross section), the energy band alignment to the underlying GaSb can be tuned by the gate voltage to be staggered (low tunneling probability) or broken-gap (high tunneling probability), thus enabling more efficient control of tunneling and enable high on-current.